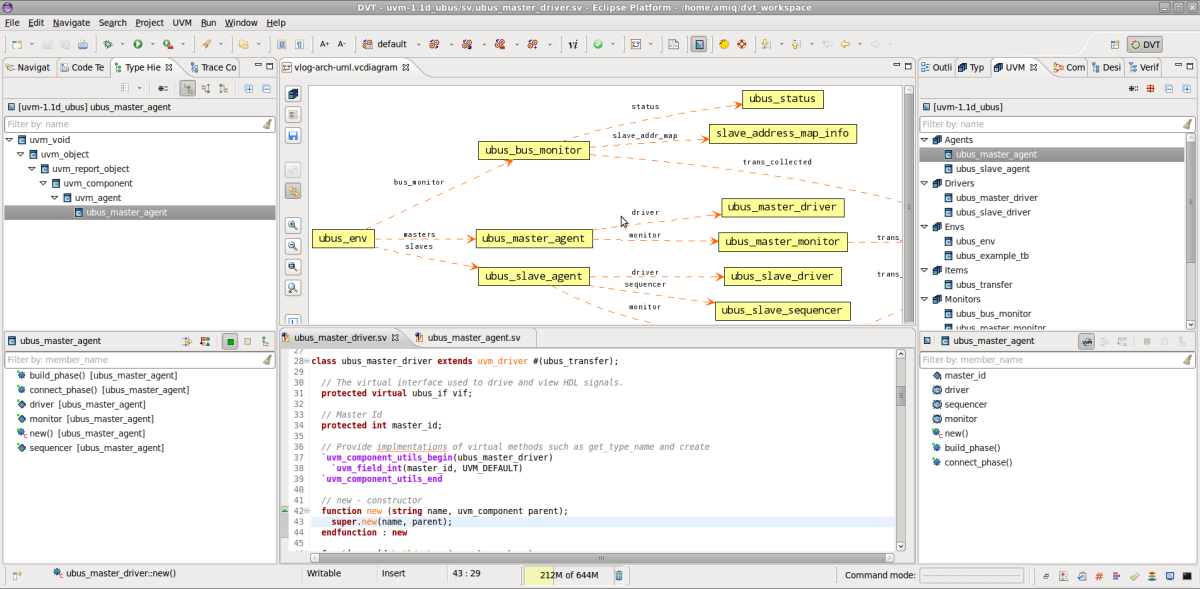

Design and Verification Tools (DVT) is an integrated development environment (IDE) for the design and verification engineers working with SystemVerilog, Verilog, VHDL, e Language, UPF, CPF, SLN, PSS, SDL. Including Universal Verification Methodology (UVM) support. It is similar to well-known programming tools like Visual Studio®, NetBeans®, and IntelliJ®. DVT comprises a proprietary IEEE standard-compliant parser, a smart code editor, an intuitive GUI, a comprehensive set of features that help with code inspection, navigation, documentation, and debugging, and an innovative linting framework. DVT allows design and verification engineers to overcome the limitations of plain text editors and use a modern and powerful tool that enables them to:

- Increase the speed and quality of new code development

- Easily understand complex or poorly documented source code

- Simplify the maintenance of legacy code and reusable libraries

- Accelerate language and methodology learning

- Automatically generate well-organized source code documentation

FEATURES

Some of the features that DVT offers include:

- Compilation errors signaled on the fly

- Autocomplete / Content Assist

- Customizable code and project templates

- Dedicated wizards to generate getters and setters, override functions, or help with UVM factory registration

- Hyperlinks

- Semantic Search and Show Usages

- Quick fixes / Autocorrect

- Refactoring

- Macro expansion

- Project database query views (types, macros, checks, etc.)

- Structural views (type hierarchy, design hierarch, call hierarchy, etc.)

- Signal tracing

- UML and TLM diagrams for inspecting and documenting the verification environment

- Schematic, trace, state machine diagrams for inspecting and documenting the design

- Dedicated UVM support

- Cross-language capabilities for mixed-language projects

- In-line reminders for task tracking (TO DOs)

- Vi and emacs emulation

INTEGRATION WITH OTHER TOOLS

Since it is built on the Eclipse Platform, the DVT IDE can be easily integrated within a large plug-in ecosystem. It also integrates seamlessly with all major hardware simulators such as NCSim , Specman , VCS , and Questa, to enable simplified simulation analysis and debugging. In addition, it works with revision control systems like CVS, Git, Subversion, ClearCase and bug tracking systems such as Bugzilla and ClearQuest.

RESOURCES

Categories: Editor, IDE, Programming Languages, Source Code Analyzer, Testing

Tags: IDE for hardware verification languages, design and verification, functional verification, SystemVerilog, Verilog, Verilog-AMS, VHDL, e language, PSS, UVM, VMM, OVM, UPF, CPF, SLN, SDL, HVL, HVLs, HDL, HDLs, Testbench, Verissimo, Specador, DVT, dvteclipse, RTL, amiq, EDA

Additional Details

Eclipse Versions: 2022-06 (4.24), 2022-03 (4.23), 2021-12 (4.22), 2021-09 (4.21), 2021-06 (4.20), 2021-03 (4.19), 2020-12 (4.18), 2020-09 (4.17), 2020-06 (4.16), 2020-03 (4.15), 2019-12 (4.14), 2019-09 (4.13), 2019-06 (4.12), 2019-03 (4.11), 2018-12 (4.10), 2018-09 (4.9), Photon (4.8), Oxygen (4.7), Neon (4.6)

Platform Support: Windows, Mac, Linux/GTK

Organization Name: AMIQ EDA

Development Status: Production/Stable

Date Created: Wednesday, April 19, 2006 - 08:00

License: Commercial

Date Updated: Friday, July 26, 2024 - 07:51

Submitted by: AMIQ EDA

| Date | Ranking | Installs | Clickthroughs |

|---|---|---|---|

| July 2024 | 393/656 | 13 | 16 |

| June 2024 | 373/681 | 20 | 44 |

| May 2024 | 425/682 | 14 | 40 |

| April 2024 | 374/687 | 22 | 29 |

| March 2024 | 380/694 | 26 | 28 |

| February 2024 | 377/687 | 22 | 281 |

| January 2024 | 432/691 | 15 | 33 |

| December 2023 | 388/671 | 20 | 19 |

| November 2023 | 320/686 | 43 | 18 |

| October 2023 | 384/673 | 24 | 25 |

| September 2023 | 357/663 | 26 | 26 |

| August 2023 | 433/673 | 13 | 17 |

Reviews Add new review

Very informative post, I

Submitted by Talha Alyas on Tue, 01/24/2023 - 05:15

Very informative post, I really get awair by SYtem Veritilog.